株式会社東栄 磁気応用部

サイトはこちら

磁気の話のはじめに

1.電荷と磁荷

2.磁気モーメントと磁性材料

3.反磁界と磁化特性

4.強磁性体

5.軟磁性材料

6.磁性材料と高周波

7.微粒子材料

8.磁気の計測

9.スピントロニクスについて

補足Ⅰ 多層膜の軟磁性

補足Ⅱ 薄膜インダクタ

補足Ⅲ 微粒子の透磁率

補足Ⅳ も一度反磁界

参考文献

磁性材料・磁気工学入門

© 2019 Yutaka Shimada

電気回路の回路定数は、L,C,R の三つです。そのうちCとRは回路素子自体の構造が単純ですが、L(インダクタ)は磁束の変化を生かす素子で、巻き線、透磁率の高い磁心が必要で、構造と作成技術がちょっと複雑です。また、その応用分野は広大過ぎて、すべてカバーした解説は不可能です。ここでは、高周波化、高密度化が止まらないICの世界に注目して、IC基板上の薄膜インダクタの研究の現状を、最近の論文を参考に紹介します。

一般に、インダクタを作ろうとすると、以下のような問題をクリアする必要があります。

- 常にΔB = 0 で、素子外の空間に磁束が広がりやすい。

- 磁束を閉じ込める、つまり、透磁率の高い磁心材料によって閉磁路を作れば、素子が小さくなる。しかし、比透磁率は、μ0=1の真空から、パーマロイ(バルク)の104(チャンピオンデータは105以上)の間にあり、電気抵抗の10-2~1022 μΩm に比べてその差は小さく、電流に比べると磁束は空間(μ0=1)に漏れやすくなっている。

- 巻き線間の浮遊容量によって C がぶら下がる、巻き線の表皮効果によって高周波抵抗損失が増加。

このような事情から、インダクタは薄膜化、高周波化が難しいのですが、これまでは、電気抵抗が絶縁物に近いくらいに高く、透磁率も比較的高いフェライト材料によって高周波化小型化がすすめられてきました。しかし、フェライトは薄膜化が難しく、現状では、フェライト焼結体の3次元的な微細加工による小型化で、およそ数 MHz まで利用できていますが、携帯電話の搬送周波数が数 GHz になっていることからもわかるように、先端技術では、数 100MHz ~数 GHz 帯で動く 2 次元的形状(薄膜状)のインダクタを必要としています。現在使われている IC 基板上のインダクタは、Cu などの導体薄膜の空芯コイルパターンです。空芯ではC、R の素子に比べて、基板上の占有面積が非常に大きくなっている上に、高周波磁束がコイルの周囲に広がるので、他の素子を近くに配置できません。これに高透磁率材料を組み合わせれば、占有面積が小さくなる、また、閉磁路にすれば外部へ漏れる磁束量が減るので、周辺配置素子の密度を上げられる、という大きな利点があります。しかし、実際にはこれが難しくて、今だに空芯コイルパターンが幅を利かせています。その理由は、今まで説明してきた軟磁性材料を振り返ると明らかです。すなわち、

- 典型的なインダクタでは、巻き線、磁心材料がありますが、薄膜化すれば巻き線の抵抗が増える、また、高透磁率磁心材料を薄膜化するには、現状では金属軟磁性薄膜しかないので、渦電流による抵抗損失が増える。つまり、2次元化(薄膜化、あるいは平板化)すると、実効的な R が大きくなり、L の性能を表す Q 値(=ωL/R)が実用できるほど上がらない。

- 第5章で説明したように、高透磁率磁性薄膜は困難軸方向で使う必要がありますが、二次元的に広がるコイルでは使い難い。

- 薄膜インダクタは、強磁性金属材料の薄膜と巻き線用薄膜から成る構造を作ることになりますが、これが、現状の半導体回路の形成プロセスに組み込むことが、どうも嫌われるのです。半導体プロセスはカッチリ組みあがってるので、材料も形成技術も異質なインダクタの製作工程を開発し、巨額な設備を半導体プロセスに組み入れて、その結果どれだけメリットがあるか、どうもリスクが大きい、空芯で行きましょう、というあたりが本当らしいです。

それでも何か希望はないか、が次の話です。

高周波基板上では、薄膜の空芯コイル使われていますが、その理由をまとめると、

「インピーダンスで見ると、ZL=jωL なので、GHz帯では数ターンのコイルで済む、つまり、占有面積の大きさと磁束のジャジャ漏れを忘れれば、数ターンの空芯の薄膜コイルパターンのL(インダクタンス)で十分使える。」ということです。

この状況を磁性材料から見ると、もし、数ターンのパタ-ンであれば、高透磁率薄膜を被せることは、半導体の世界でも、そんなに面倒なことではないかもしれない。しかし、磁性薄膜材料がGHz帯で低損失にできるか、が問題です。この辺りは、磁気工学の専門家たちにとって、興味深いテーマなので、これまで多くの試作研究が発表されてきましたが、上記のように磁性材料の損失が大きくなってQが上がらない、などの問題で、磁気関連の学会で発表するにとどまっています。

しかし最近、磁気工学の専門家ではなく、CMOSの研究グループ(Intel Co、アリゾナ州立大)からの発表があり(参考文献 Ⅱ—1~7)、IC用に開発された、実用に近い薄膜インダクタとして注目されています。ここではその一連の発表の概要を、このHPの内容を基礎知識として使って解説し、「磁性材料入りの薄膜インダクタ」も、まだまだ捨てたものでもない」ことを紹介することにします。

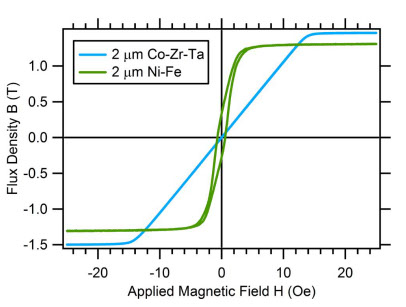

図Ⅱ-1は、磁心材料として使ったCo-Zr(4at%)-Ta(4.5at%)薄膜とNi-Fe(20at%)薄膜のB-Hループ(困難軸方向)の例です(参考文献 Ⅱ—3)。

図Ⅱ-1

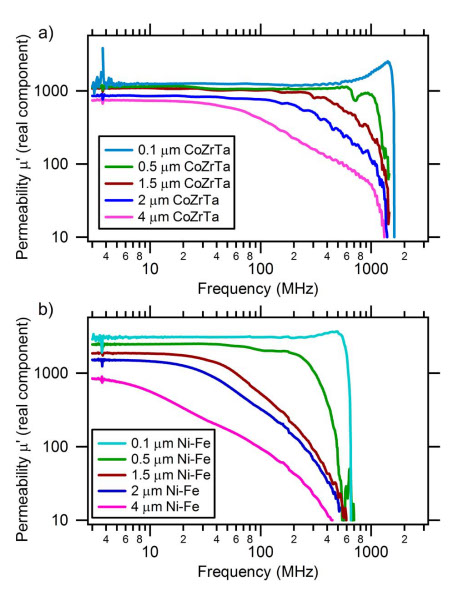

第5章で説明したように、アモルファス合金やNi-Fe合金では、磁界中熱処理によって均一な一軸磁気異方性(誘導磁気異方性)を作ることができます。Co-Zr-Ta(図5-15(b)、CZTとします)では、Hk ~ 15Oe、Ni-Fe では Hk ~ 3Oe になります。図の Ni-Fe は、困難軸方向でもループが膨らみ、Hc も大きくなっています。これは、磁気異方性が弱いので、容易軸の方向と強さの均一性が悪いからです。これに対して、Hk が 15Oer の CZT では Hk の分散( Hk 強さと方向が場所によって異なる)が小さいので、困難軸方向では直線になります。図Ⅱ-3は、いろいろな厚さの試料の初透磁率の測定例です(参考文献 Ⅱ—3)。

図Ⅱ-2

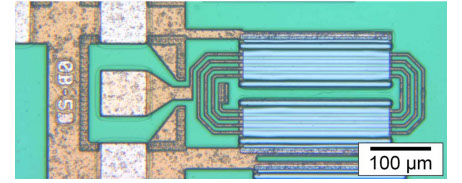

第6章では、薄膜の困難軸方向の高周波透磁率の式を紹介し、高周波での初透磁率は、Hk、電気抵抗、厚さに依存することを説明しましたが、図の実験結果は、これをよく表していて、透磁率(μ’)が厚い試料で低下するのは渦電流が原因で、Ni-Fe の低下が顕著で、また磁気共鳴周波数(μ’ が消失する点)が低くなります。これは、Ni-Fe の電気抵抗(5~10μΩcm)が CZT の電気抵抗(約150μΩcm)に比べて低く、また Hk も弱いためです。それで、GHz に近い周波数で高い透磁率を保つには、CZTの0.1μm以下の薄膜で困難軸方向のみが使えることになります。通常の二次元的に広がったコイルでは、コイル電流による磁界が平面全方向に分散するので困難軸方向のみを使うのは難しいですが、ここでは、図Ⅱ-3のように、長方形のコイルにすることで解決しています(参考文献 Ⅱ—3)。

これは、磁性体の透磁率が利用できれば、わずかなターン数で済むこと、磁性体をコイル全面でなく一部に付ければ十分であると、割り切っているわけです。

図Ⅱ-3

ここでは、インダクタンスを上げるにはもっと厚い薄膜(0.5~1μm)が必要なので、「補足Ⅰ 多層膜の軟磁性」で説明した、絶縁性の中間膜を使った多層膜を使います(参考文献 Ⅱ—5)。

図Ⅱ-4

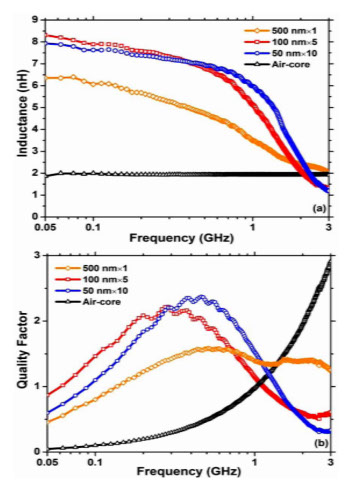

図Ⅱ-4は、図Ⅱ-3の構造で、総厚 0.5μmの多層膜を使ったインダクタンスの多層構造と Q 値の測定結果です。多層構造が細かくなると(層数が多くなると)、渦電流損失が低下し、1GHzくらいまでQ 値が空芯コイルよりも高くなり、インダクタンスは空芯に対して4倍位になっています。次は、もっと改良する方法についてです。

図Ⅱ-5

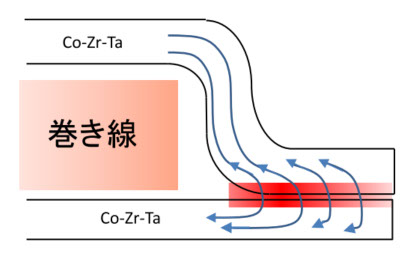

二次元的インダクタの巻き線の周囲を磁性体で囲むときに、巻き線の上と下の磁性層を単純に広い面積で重ねればOKと考えるのが普通ですが、この研究では、ここが高周波損失の主因であることを突き止めて、しつこく追及しいます。図Ⅱ-5は、単なる説明図ですが、上下の膜の重なる部分には磁気的には無視できないギャップがあり、透磁率が大きく低下して(磁気抵抗が大きくなって)います。磁気抵抗を下げるためにギャップの幅を大きくすればインダクタンスは増えますが、そうすると、渦電流の起こる面積(図の赤い部分)が広がるので、損失が増える、という関係にあり、薄膜インダクタの特性劣化の主因になっています。

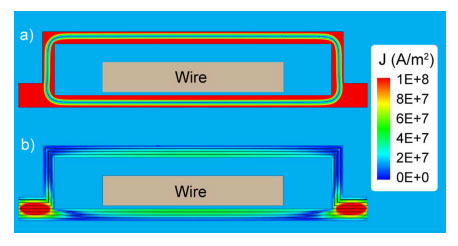

図Ⅱ-6 は、シミュレーションの結果で(参考文献 Ⅱ—3)、磁性薄膜内を流れる渦電流の密度分布です。a) は、単層膜の場合で、大きな渦電流が全体に生じていますが、b)では、ギャップの部分を除いては、渦電流が多く低下しています。しかし、ギャップの部分では、図Ⅱ—5に示したように多層膜の効果がなく、大きな損失があることがわかります。

図Ⅱ-6

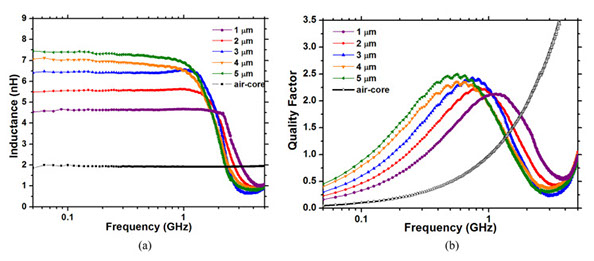

図Ⅱ-7は、このギャップの幅を変えた実験です(参考文献 Ⅱ—6)。ギャップ幅が広いほどインダクタンスは大きくなり、Q 値はあがりますが、同時に損失も増えるので、Q 値のピークは低周波側に下がります。ギャップ幅が狭くなれば磁気抵抗は上がるので、インダクタンスと Q 値は下がりますが、損失は低下して Q のピーク周波数は上がります。

図Ⅱ-7

このように、薄膜インダクタの性能を決める支配的要因は、意外なところにあった、というのが、この研究の面白いところです。また、ギャップ幅を大きくしたままで渦電流を下げる方法として、ちょっと奇策ですが、図Ⅱ-8のように、ギャップに切込みを入れて渦電流の広がりを抑えています(参考文献 Ⅱ—6)。

図Ⅱ-8

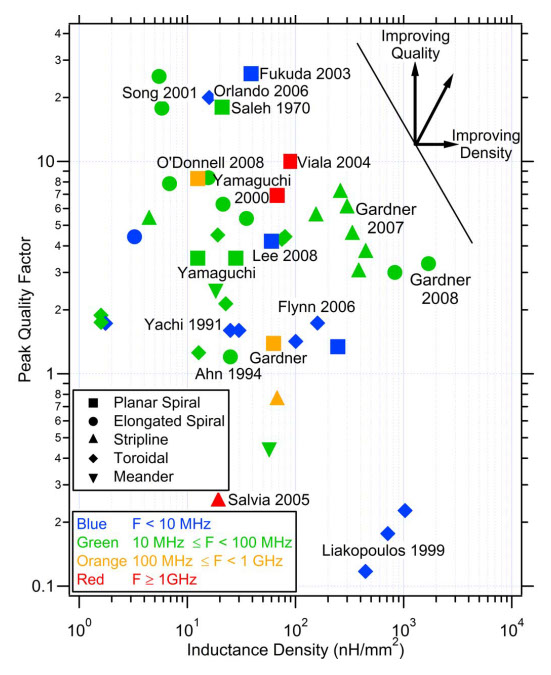

図Ⅱ-9は、2009年頃までに発表された平面インダクタ(必ずしも薄膜でないが、2次元的な構成)の、インダクタンス密度(単位面積mm2上につくったインダクタンスの大きさ)と Q 値の関係です(参考文献 Ⅱ—3)。如何に多くの研究者が、IC インダクタの夢を追い続けたか、わかる思います。これに見られる傾向は、インダクタンス密度が上がると熱損失(抵抗損失)が大きくなり Q 値が低下すること、つまり高透磁率磁性材料を増やして磁気回路を厚くすると、渦電流損失が増えるということです。図中の ● と ▲ は、上記のインダクタの例です。Q 値は幾分下がっていますが、インダクタンス密度は大きくなり、IC 上のインダクタとしては十分な大きさと主張しています。

図Ⅱ-9

以上が、CMOSプロセス用に開発した薄膜インダクタです。その要点は、

1)全ての磁性薄膜が困難軸方向で働くような構成にした

2)コイルを磁性薄膜で覆う構造、

3)多層膜を使い、最適化した、

4)ギャップ付近の損失が大きいことを見出し、切込みによって損失を低下させた。

等です。

これまで、平面状のインダクタを作るには、コイルパターンを作って、その上に磁性膜、またはフェライト薄板を被せる、というのが一つの方法でしたが、理論計算(参考文献 Ⅱ—8)によると、上下の一面のみが高透磁率材料で覆われた場合には、インダクタンスの増分は最大で100%、つまり2倍にしかならないことがわかっています。磁性材料の効果をもっと上げるには、巻き線を磁性材料で囲む、つまり閉じた磁気回路をつくる必要があります。ここでも、巻き線を薄膜で閉じた磁気回路を作るために、図Ⅱ-5のように上下の膜を端部で重ねておりますが、実は、これで生じたギャップ部分の損失が、このインダクタ開発の最大の問題点であることを指摘した、というのが、上記の文献の成果の一つと言えます。単純な話に聞こえるかもしれませんが、これまでの薄膜インダクタでは損失が大きすぎて、このような問題点を掘り下げることができなかった、ということです。

以上が、CMOSプロセスに適合できると主張している薄膜インダクタの概要ですが、さらに性能を上げるにはどうするか、渦電流を減らすには、電気抵抗を上げればいいのですが、現状では、金属薄膜軟磁性に匹敵するような絶縁性の磁性体は作られていません。フェライトは,絶縁性に近い高電気抵抗の材料ですが、軟磁性を得るための組成、結晶構造、また、その焼成条件が複雑で、気相成長による作成(蒸着、スパッタなど)が難しく、軟磁性フェライト薄膜としては、実用段階に達してはいません。また新規な例として、化学反応によるフェライト薄膜(参考文献 Ⅱ—9)があり、軟磁性フェライト薄膜を比較的容易に作れる方法として画期的なものですが、Hk の制御と再現性がもう一歩というところです。さらに、第5章のグラニュラー薄膜は、電気抵抗が金属薄膜よりも1~2桁高く、さらに高いものが得られる可能性も原理的に否定できませんが、磁場中熱処理が必要なものも多いので、CMOSのプロセスに組み込めるかどうかは不明です。

以上のように、インダクタの薄膜化は、極めて魅力的なテーマではありますが、CMOSのような実用プロセスと、磁性材料を利用したインダクタ作成のプロセスがマッチしない、あるいは、CMOSの専門家と磁気工学の専門家のマッチングの努力が足りないのが、話がすすまない原因のようです。ここで紹介したIntel Co.の研究も、いよいよ実用化研究の段階になって地下に潜ったか、止めてしまったのか、その後の発展状況を調査しても、あまり情報がありません。この問題を何とかしようとする挑戦者が、次々と現れることを期待したいところです。

▲ページ上部へ